12月6日,RISC-V峰会在美国旧金山召开,中国科学院的相关科研人员也参加了会议。

据国外媒体报道,中国科学院正在政府的支持下,开发开源RISC-V性能处理器。中国科学院表示,希望在芯片设计企业加速发布产品的风口下,能够给RISC-V开源项目提供带动和支持力量。同时,中国的开源RISC-V性能处理器芯片每六个月就会发布一次重大升级。

RISC-V是一个基于精简指令集(RISC)原则的开源指令集架构(ISA),所有企业和实体都可以使用,而不需要支付任何版税。

之所以升级周期是六个月,这与创建指令集的RISC-V基金会批准新功能的速度加快有关系。

国外媒体报道,中国政府已经将半导体芯片产业作为赶超美国的突破口,还支持采用ARM设计、制造的芯片。前段时间,阿里达摩院已经在其云服务器上部署了平头哥系列RISC-V 服务器芯片,并对一些设计进行了开源。

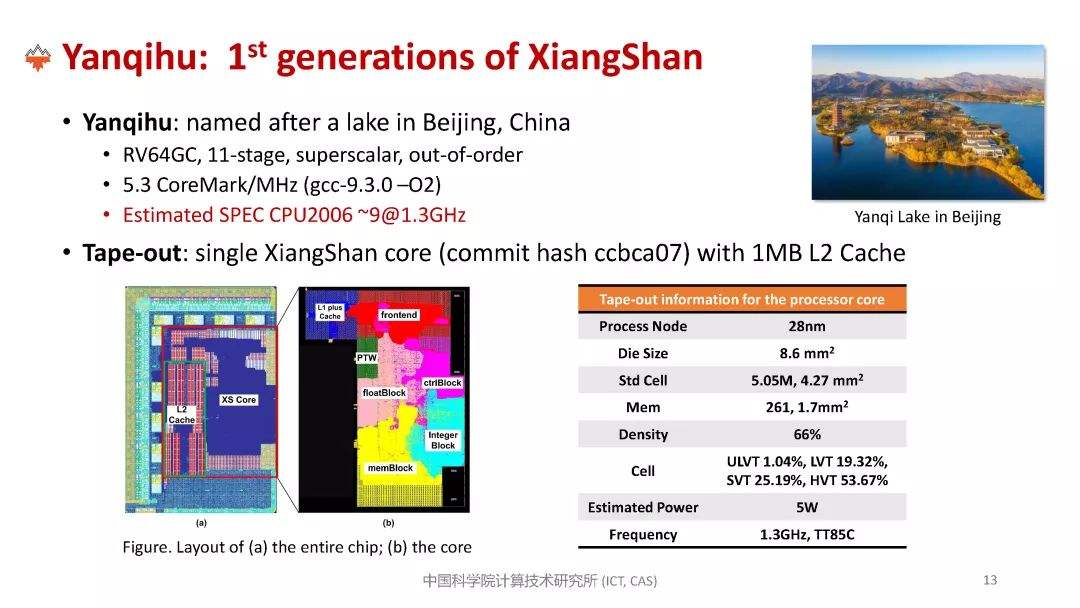

中国科学院此前发布了香山系列芯片的首颗,并将其命名为雁栖湖。雁栖湖在今年七月份成功流片,同时针对28nm工艺进行了优化。雁栖湖已经被英国ARM公司当作主要竞争对手,直接与其Cortex-A76内核的处理器芯片形成竞争。

雁栖湖的下一代芯片已经被研发出来了,并命名为南湖。南湖芯片由中芯国际采用14nm工艺制造,并基于64位RV64GCBK设计,同时支持新拓展功能。

国外媒体表示,南湖芯片的一些新功能借鉴了SiFive设计,比如Block Inclusive Cache。

在测试中,南湖芯片相比其上一代的雁栖湖,各项指标都提升了近2倍。南湖芯片被设计成以2.0GHz的速率运行,而雁栖湖的设计速率只有1.3GHz。并且南湖芯片是双核处理器,雁栖湖只是单核的。

鄂公网安备 42011502001385号 鄂ICP备2021012849号

鄂公网安备 42011502001385号 鄂ICP备2021012849号