最近公布的一项专利技术表明,英特尔正在研究一种新的晶体管设计---堆叠叉板(Forksheet)晶体管。

堆叠叉板晶体管可以实现垂直堆叠的3D CMOS结构,相比目前最先进的三栅极设计,虽然也很难缩小晶体管的体积,但可以增加更多的晶体管数量。

该项专利技术主要是对纳米带晶体管与锗原子薄膜进行配对使用,锗原子薄膜充当了介电壁。锗原子薄膜对垂直堆叠的各层晶体管进行了物理分隔,充当p-栅极沟槽和n-栅极沟槽之间的绝缘体。通过这种设计,可以使NMOS器件和PMOS器件排列的更加紧密,且不影响各自的功能,这样就可以节省出更多空间,也就是说,可以增加更多的晶体管数量。

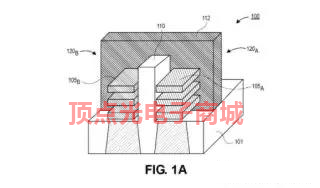

英特尔堆叠叉板(Forksheet)晶体管

早在2019年,英特尔就在一次电子设备展上展示了该技术。当时,该技术还处于探索阶段,任何关于堆叠叉板技术是如何提高晶体管密度、性能和效率的具体数据都无法找到。

不过,英特尔并不是唯一一家研究该技术的公司。比利时微电子研究中心(IMEC)的一个研究小组也在同一年宣布,他们研究得到了一个专门用于堆叠叉板设备的标准单元模拟数据。IMEC的研究数据是在英特尔这项专利的基础之上进行的。

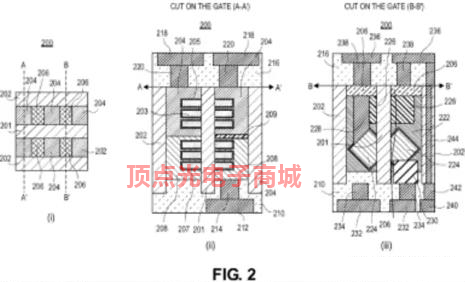

堆叠叉板晶体管的平面图和横截面图

比利时微电子研究中心的标准单元模拟数据表明,相比传统纳米片技术,当采用2nm技术节点时,堆叠叉板晶体管技术可以显著提高晶体管的密度。这表明,在2nm及以下技术节点,堆叠叉板晶体管技术可以大幅提升芯片的性能,尤其是在不同晶体管架构需要考虑精确的蚀刻分辨率的时候。

比利时微电子研究中心(IMEC)

英特尔的研究时间是非常充裕的,对堆叠叉板晶体管技术的研究至少持续到了2020年6月。虽然我们现在还不知道英特尔是否会选择堆叠叉板架构来进行2nm工艺的研发,但既然英特尔已经公布了该项技术专利,就肯定已经规划好了该项技术的使用目的。

鄂公网安备 42011502001385号 鄂ICP备2021012849号

鄂公网安备 42011502001385号 鄂ICP备2021012849号